| | Categorie Articoli | | > Prove | | > Attualitŕ | | > Approfondimenti | | > Interviste | | Altro su HIRC | | > Segnalaci una notizia | | > Advertising | | > Forum |  | | Ultime dal forum | | Visualizza HIRC del | | |

| | Element Interconnect Bus, interfaccie di I/O e memoria | Il termine broadband che compare nel nome dell’architettura non č certamente casuale, infatti tutto č dimensionato per evitare che si formino colli di bottiglia nel trasferimento di dati ed istruzioni, sia tra i componenti interni del processore che nel dialogo con l’”esterno”. L’adozione dello schema che vedremo č fondamentale per lo stream processing da un lato e per il calcolo distribuito dall’altro.

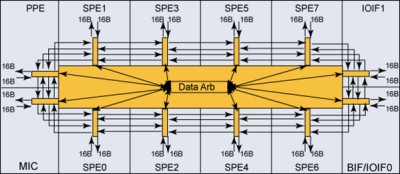

La base che consente di utilizzare con profitto lo stream processing tra le varie SPE č senza ombra di dubbio il bus EIB (Element Interconnect Bus), un bus ad altissima velocitŕ che collega tra loro PPE, SPE, memory controller ed interfaccia di I/O.

| | Diagramma dell'EIB: un ring bus con 4 canali da 128 bit |

Si tratta di un ring bus con 4 canali da 128-bit ciascuno, funzionante alla metŕ della frequenza del processore, e capace di eseguire 3 transazioni contemporaneamente. Teoricamente č in grado di trasferire 96 byte per ciclo di clock del processore (192 byte per ciclo del bus, per una banda massima teorica di quasi 400GB/s a 4GHz). Secondo IBM perň nella realtŕ il transfer rate effettivo sarŕ pari solo circa il 70% di quello teorico.

L’utilizzo di un ring bus (il quale si ispira alle reti token ring) introduce anche un parametro di localitŕ alla programmazione in modo da poter sfruttare al meglio la capacitŕ di trasmissione disponibile: se ad esempio varie SPE devono cooperare e devono scambiarsi dati, č importante che gli scambi avvengano tra unitŕ adiacenti, in modo da ridurre al minimo la porzione di bus occupata, aumentando la probabilitŕ di riuscire a sfruttare fino in fondo il parallelismo dei trasferimenti.

Per ciň che riguarda il dialogo con il mondo esterno, sia i 2 memory controller che le 2 interfacce di I/O sono state sviluppate in collaborazione con Rambus. L’integrazione del memory controller on-die (come avviene con i processori della famiglia AMD64) consente di ridurre drasticamente i tempi di accesso, nonché di liberare il bus di sistema da un ingente flusso di informazioni, e di poterlo cosě dedicare ad altri scopi.

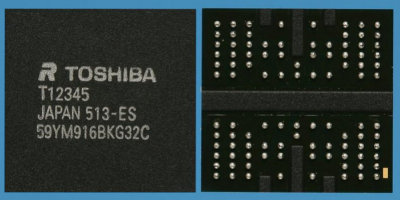

| | Il primo chip di memoria XDR Toshiba |

In particolare, i memory controller supportano le nuove memorie XDR di Rambus, capaci di trasferire su ogni linea di collegamento 8 bit per ciclo di clock. Ciascun controller č in grado di trasferire fino a 12,8 GB/s, per un’ampiezza di banda aggregata superiore ai 25GB/s, paragonabile a quella di una scheda grafica di fascia medio/alta.

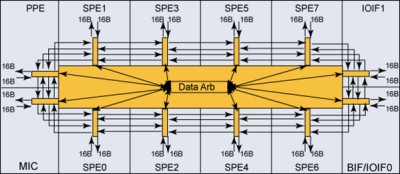

Infine l’interfaccia di I/O, chiamata FlexIO e sviluppata anch’essa da Rambus, ricopre un ruolo fondamentale per il calcolo distribuito, infatti mette a disposizione, tramite due canali indipendenti, un’ampiezza di banda complessiva di 76,8 GB/s per il collegamento delle periferiche e, soprattutto, di altri processori Cell; č possibile realizzare numerose configurazioni, come mostrato in figura, tuttavia č particolarmente interessante l’implementazione biprocessore, che puň essere realizzata in modalitŕ “glueless” senza l’utilizzo di alcuno switch o altra logica aggiuntiva.

| | Possibili implementazioni di sistemi multi-CPU basati su Cell |

La presenza di una interfaccia di collegamento cosě veloce, consente di pensare allo stream processing ad un livello ancora piů alto, dove ogni processore, o piů cluster di processori eseguono una elaborazione complessa, presentando il risultato in uscita per ulteriori elaborazioni.

|

Vuoi segnalarci una tua notizia? Clicca qui!

| | | Comments | | | | Annunci | | | Attualitŕ | | Fujitsu presenta la soluzione e roadmap Mobile WiMAX System-on-chip | | Nuovo masterizzatore DVD esterno Sony DRX-820UL | | Nokia 770 Internet Tablet e Google Talk insieme | | Core 2 Duo, gioco di parole per i nuovi processori Intel | | Recensione Crucial Gizmo! Overdrive 1GB online | | LCD con tempo di risposta di 2ms da Acer | | ATi ha acquisito la finlandese BitBoys | | AMD ritira 3000 CPU Opteron difettose | | Intel punta decisa verso i 32 nanometri | | Intel vPro: nuova piattaforma per PC aziendali | | Prove | | Crucial Gizmo! Overdrive 1GB: capacitŕ e prestazioni | | Crucial Gizmo!: 1GB per foto, musica e pinguini | | Raffreddamento a liquido: quando il gioco si fa duro | | Sapphire Radeon X1300: alta definizione per tutti | | Enermax Liberty 500W: la libertŕ fatta alimentatore | | Genius Ergo 300: mouse piccolo ma non troppo | | Royaltek GPS RBT 2001 | | Crucial Ballistix Tracer DDR500: semplicemente estreme | | HP Business Desktop dx5150: potenza per ufficio | | Dal Radeon X600 all'X800: generazioni a confronto in casa Sapphire | |

|