| | Categorie Articoli | | > Prove | | > Attualitŕ | | > Approfondimenti | | > Interviste | | Altro su HIRC | | > Segnalaci una notizia | | > Advertising | | > Forum |  | | Ultime dal forum | | Visualizza HIRC del | | |

| | Cenni alla gestione delle interruzioni | La gestione delle interruzioni su un processore Cell č leggermente piů articolata rispetto a quella dei processori tradizionali, infatti essendo presenti su un chip piů entitŕ incapaci di gestirle (le SPE), č necessario che queste vengano inoltrate al PPE, che poi provvederŕ alla loro gestione.

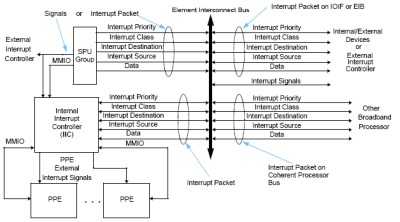

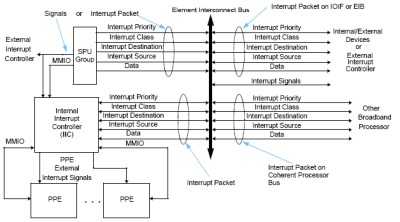

Per realizzare questo meccanismo senza penalizzare le prestazioni, č stata approntata una soluzione particolarmente efficiente: il PPE č dotato del classico sistema di gestione delle interruzioni tipico delle architetture PowerPC, a questo perň si aggiunge l’IIC (Internal Interrupt Controller) che č un componente destinato a raccogliere le eccezioni generate dalle SPE, o dalle periferiche (le cui comunicazioni passano sempre attraverso l’EIB), ad analizzarle ed a ordinarle in base alla prioritŕ. Una voltŕ fatto ciň l’IIC inoltra le interruzioni all’”External” Interrupt Controller integrato nel PPE.

| | La gestione delle interruzioni sul Cell |

Ovviamente mentre viene servita una interruzione, questa puň essere interrotta a sua volta solo da una interruzione di prioritŕ maggiore. Il grafico seguente permette di schematizzare chiaramente la situazione:

Interessante notare che le interruzioni, in un ambiente multiprocessore, possono “nativamente” giungere anche da altri Cell, questa considerazione permette di scendere ulteriormente nel dettaglio dei sistemi multiprocessore e del calcolo distribuito.

Se ad esempio consideriamo la configurazione piů semplice (due soli Cell), uno dovrŕ essere impostato come master e l’altro come slave; alcune operazioni di servizio, come appunto la gestione delle interruzioni faranno capo unicamente al master, semplificandone notevolmente la gestione e permettendo di pensare al processore slave come una vera e propria estensione del master.

|

Vuoi segnalarci una tua notizia? Clicca qui!

| | | Comments | | | | Annunci | | | Attualitŕ | | Fujitsu presenta la soluzione e roadmap Mobile WiMAX System-on-chip | | Nuovo masterizzatore DVD esterno Sony DRX-820UL | | Nokia 770 Internet Tablet e Google Talk insieme | | Core 2 Duo, gioco di parole per i nuovi processori Intel | | Recensione Crucial Gizmo! Overdrive 1GB online | | LCD con tempo di risposta di 2ms da Acer | | ATi ha acquisito la finlandese BitBoys | | AMD ritira 3000 CPU Opteron difettose | | Intel punta decisa verso i 32 nanometri | | Intel vPro: nuova piattaforma per PC aziendali | | Prove | | Crucial Gizmo! Overdrive 1GB: capacitŕ e prestazioni | | Crucial Gizmo!: 1GB per foto, musica e pinguini | | Raffreddamento a liquido: quando il gioco si fa duro | | Sapphire Radeon X1300: alta definizione per tutti | | Enermax Liberty 500W: la libertŕ fatta alimentatore | | Genius Ergo 300: mouse piccolo ma non troppo | | Royaltek GPS RBT 2001 | | Crucial Ballistix Tracer DDR500: semplicemente estreme | | HP Business Desktop dx5150: potenza per ufficio | | Dal Radeon X600 all'X800: generazioni a confronto in casa Sapphire | |

|